1. 要約

一般的な電流モード降圧DC/DCコンバータ・アプリケーションにおいて、位相補償定数を計算で求める一例を紹介し、実際に簡単な計算式とシミュレーションで評価・確認しながらそのアプローチ法を学びます。これはパワーステージで作られるポールとゼロに対して、誤差アンプ(及び補償器で)それらをキャンセルするゼロとポールを作るというアプローチです。

2. 本ノートの目的と読者層の想定、位相補償とは

DC/DCコンバータの位相補償は少々分か難い分野かと思われます。DC/DCコンバータを学び始めた人向けに、この基本理解ができることを目標とします。

本例での位相補償設計とは下図の部分のRとCの値を決めることです。

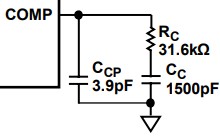

端子名としては、COMPやVc, Ithと表現している製品もありますが、基本的に全て同じモノと考えて良いです。このR,C部品をIC内部に予め内蔵している製品もあります。μModule製品やモノリシック製品に多い傾向にあり、それらは基本的にはこれを設計する必要はありません。従いまして可能であればそれらを第一候補に選定されることを推奨いたします。またLTpowerCADツール等で設計ガイドを得られる、またはデータシートに設計データや式が得られるものはそれらに従います。しかしながらそのどちらも得られない場合は、本ノートが基本設計のガイドとなり得ることを期待します。また内部位相補償の製品でもユーザーが定数を選べる様な製品も有りますので、そういった場合も補償の知識は有益と言えます。(例:MAX77504 下図参照)

題材としては位相補償に関する情報が比較的多いと思われる降圧の電流モードの製品 (ADP2384) のデータシート情報を、ツールとしてはLTspiceを使いながら実際の計算やシミュレーションを行いながら進めます。※1

基本的な電力段の設計(出力電圧設定、Fsw, L, Cの選定等)等が正しく終わっている事とLTspiceツールの基本的な使用法を知っている事を前提としています。小信号ACモデルを基に検討・計算・設計を行い、最後に過渡(時間)解析でも位相・利得余裕のFRAシミュレーションと負荷過渡応答の検証を試みます。

※1 ADP2384にはエクセル設計ツールやEE-SIM OASISモデルが利用できる様ですが筆者がこれらに慣れていないという理由で本稿ではLTspiceツールで行います。

LTspiceに慣れていない方向けに、LTspice入門資料を無料で配布しております。 基本的な操作方法やシミュレーションの進め方を解説していますので、以下のページからダウンロードいただけます。

Analog Devices(アナログ・デバイセズ)のご紹介 | | ソリューションから探す | 製品情報 | ダイトロン株式会社

3. 全体小信号モデル図の準備とその説明

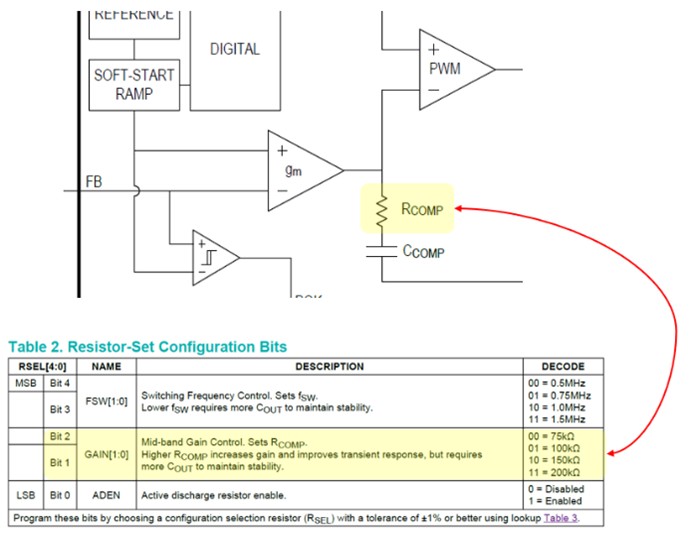

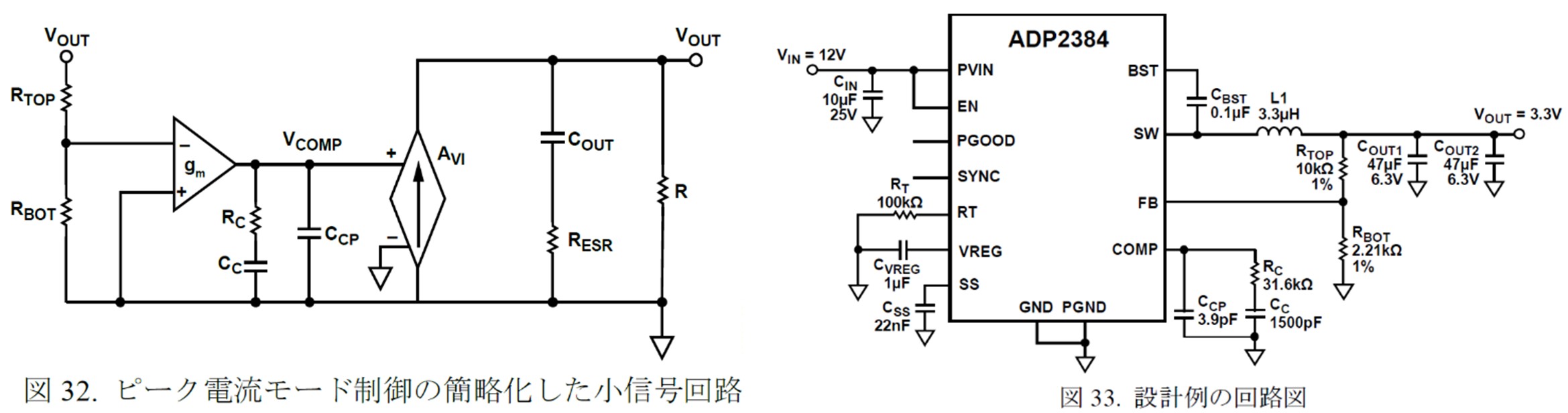

今回の題材としてADP2384のデータシート情報を取り上げます。データシート17ページには簡略化した小信号回路 図32があり、これを図33の3.3V出力の回路図例で検討します。

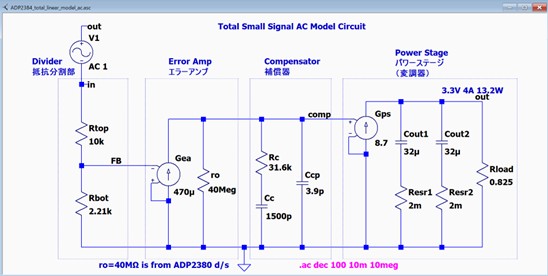

小信号回路をLTspiceの回路図にしたものが下図です。

AC解析に不要な Vref, Lはこの図では省略しております。この様に電流モードにおける簡易モデル化ではLは無いものと見なされ、電流源の一部に変わったと言えます。従いまして電圧モードに見られる様にパワーステージでのLC共振は無く、シンプルな1次応答となります。※2

この図は大きく3つの部分に分けられます。左から抵抗分割部、真ん中がエラーアンプと補償器、右がパワーステージです。

※2 リファレンス資料に有るAN-149に拠るとこのパワーステージの電圧制御電流源のシンプルモデルは、スイッチング周波数の1/50程度までの位相特性はほぼ正確と述べられています。

各部品とノード名の内容は下表です。

| 名前 | 内容 | 単位 |

| V1 | ループゲイン測定用のAC電圧注入信号源 | |

| Rtop Rbot |

出力電圧設定用抵抗(今回はこれらの抵抗には並列に容量は入れておりません)Vout=Vref のアプリケーションにおいては抵抗分割部は無く、この部分でのゲインは1です。最近のサイレント・スイッチャー3等はそうです。その場合はRtop=0、Rbot=∞と考えます。 | Ω |

| Gea | 電圧制御電流源形式のエラーアンプ: EA(トランスコンダクタンスアンプ)通常のオペアンプの様な電圧出力形式ではありません。ごく一部の製品で電圧出力形式のも見かけられますが、殆どが電流出力タイプです。負帰還サーボループの主要部品です。14. 付録の3)に関連情報を載せています。 | A/V (S) |

| ro | EAの出力抵抗。デバイス内部固定値で位相補償にはあまり関係しません。Ccと共に低周波ポールを形成します。抵抗値が高い方がDCゲインが高くなり、出力電圧精度は高まります。 | Ω |

| Rc、Cc、Ccp | 補償器(これが今回の設計ターゲット)トポロジーや構成によっては Ccpは不要な場合が有ります。本例では付けております。上記の回路図での数値は計算理想値に最も近いE96系列の標準部品値の値を書いています。Rtop, Rbotに付いても同じです。 | Ω、F |

| Gps | 電力段(パワーステージ)電圧制御電流源、modulator (モジュレータ・変調器)とも呼ばれる事があります。ADP2384 データシートではAviと書かれている菱形の部分です。 | A/V (S) |

| Cout | 出力コンデンサの実効容量値(公称定格容量値ではありません。DC電圧重畳された後の容量値です。)今回の例では公称容量 47µF のセラミックコンデンサを実効容量 32µF としています。 | F |

| Resr | 出力コンデンサの実効直列等価抵抗値 | Ω |

| Rload | 負荷抵抗(Rload = Vout / Iload ) | Ω |

| FB | エラーアンプ入力端子 | |

| comp | compensation(補償)端子。エラーアンプ出力端子、またパワーステージの制御入力端子でもあります。補償器で補償された電圧で後段のパワーステージを駆動します。このノード電圧は車のエンジンで例えるとアクセルペダルの様なものです。 | |

| Out | 最終の出力端子 | |

| In | 負帰還入力端子。通常のアプリでは出力端子と接続されます。 |

下図はこの図には表れていませんが重要な部品と用語・定義等です。

| Fsw | スイッチング周波数 | Hz |

| 1/2・Fw | スイッチング周波数の1/2です。GM(ゲインマージン)を判定する周波数になります。GM ≥ 8dBが望まれます。 | Hz |

| Fco | 目標クロスオーバー周波数(本例ではFsw/10が目標) | Hz |

| Vref | 内部リファレンス電圧:0.6V ~ 1.2V 程度が多いです。ADP2384 では0.6V です。 | V |

| Av(fb) | 抵抗分割部のゲイン | V/V |

| Av(ea) | エラーアンプと補償器部のゲイン | V/V |

| AV(ps) | 電力部(パワーステージ)のゲイン | V/V |

4. パワーステージ(電力段)

電力段の周波数特性を把握、計算します。 RloadとCoutで作られるポール周波数 fp(ps) は、

Resr とCoutで作られるゼロ周波数 fz(ps) は、

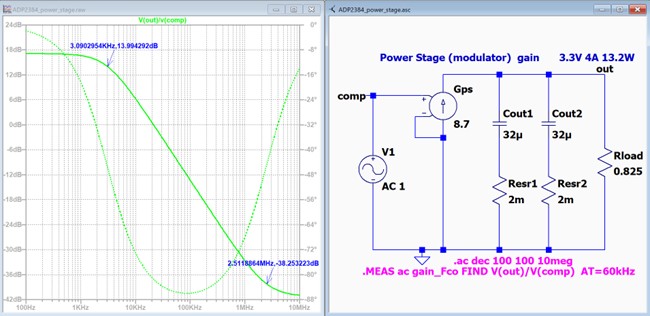

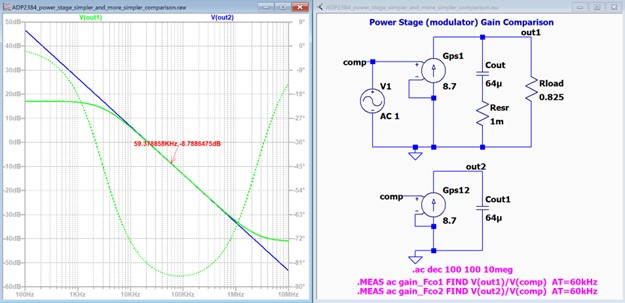

下図はこのパワーステージの周波数特性をACシミュレーションしたものです。

今回の例では、上式で計算した電力段のポールとゼロ周波数に対して補償器でポールにはゼロを、ゼロにはポール周波数をそれぞれ作り、キャンセルするという最もシンプルな設計アプローチをとります。(別のアプローチも有り、別編で解説を検討中です)

5. パワーステージのFco(60kHz)に於けるインピーダンスとゲインを計算する

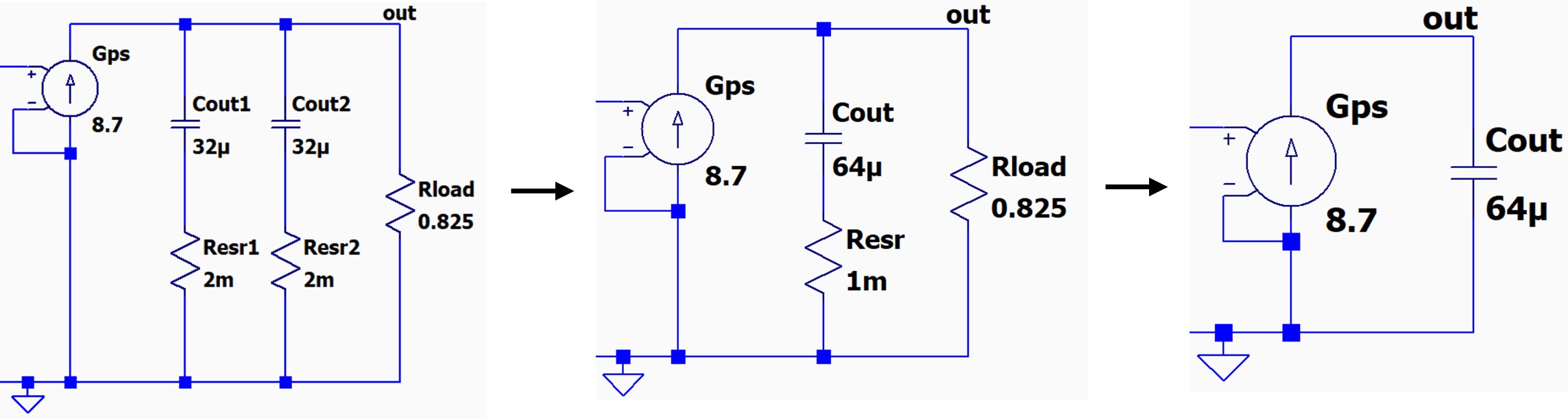

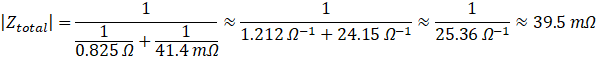

交流回路のインピーダンス計算の復習をしながら、CoutとRloadの並列回路で作られる合成インピーダンスを計算してみましょう。 このパワーステージ2個の並列のCoutを1個と考えてもう少し整理・簡単に表すと真ん中の図になります。

CoutのFco (60kHz) におけるリアクタンスは、

![]()

これと、Resr (1mΩ) の直列合成インピーダンスはベクトルの2乗和で計算できます。1mΩは41.1mΩと比べるとほぼ無視できそうに思われますが、一応計算してみますと、

デシベルで表現すると、

ResrとRloadを無視したものとのシミュレーション比較も行ってみましょう。上の回路図がResrとRloadを含むもの、下が含まないものです。グラフのカーブは緑色が上の回路図、青色が下です。

この様にFcoの60kHzに於いての差はほぼ見えません。 まとめるとパワーステージのゲイン Av(ps) は Gps * (Cout のインピーダンス) つまり

というシンプルな掛け算で簡略化出来るという事です。

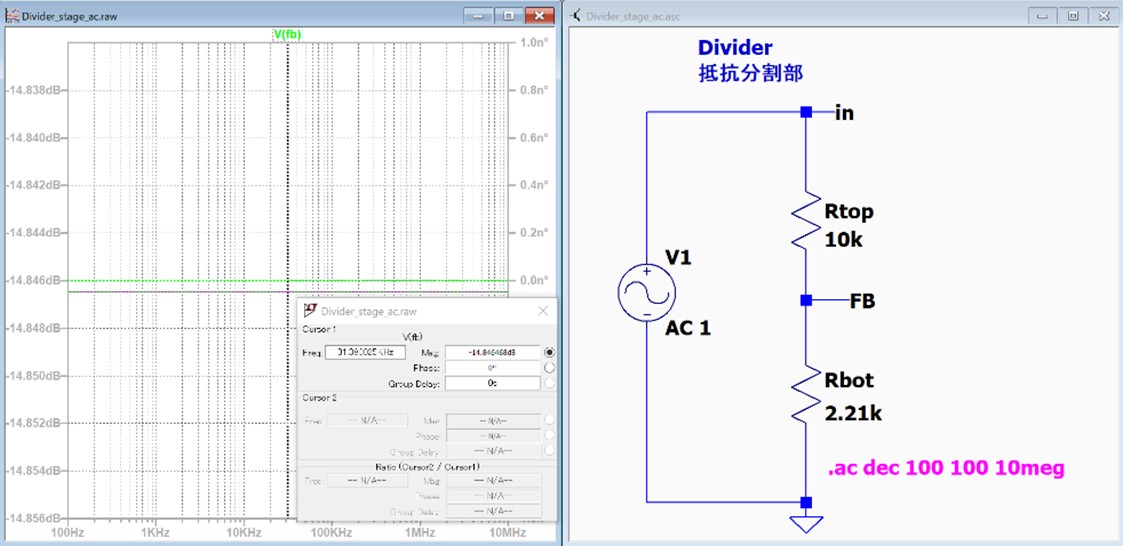

6. 抵抗分割部

出力電圧設定用の抵抗分割部の検討を行います。今回は並列にコンデンサは付けておりませんので、ゲイン・位相共に周波数特性は有りません。

この部分のゲイン Av(fb)は、

![]()

![]()

と計算できます。

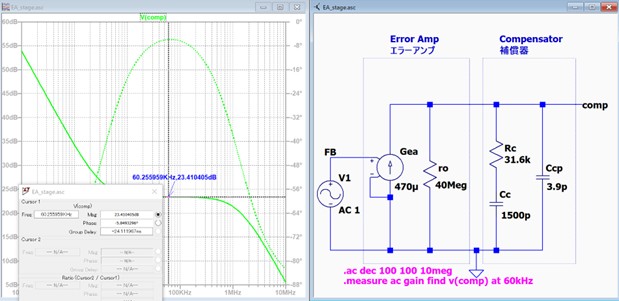

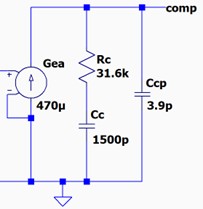

7. エラーアンプと補償器

先のパワーステージで書いている様にパワーステージのポールには補償器のRcとCcの直列回路でゼロ周波数を作ります。つまり

![]()

です。

同じ様にパワーステージのゼロには補償器の RcとCcp の並列回路でポールを作りますので、

です。つまり Cc とCcp は Rc が決まれば、計算できることになります。

それでは、Rc はどの様に決めるのでしょうか?

その答えはこのエラーアンプと補償器のステージのゲインを幾らにしたいのかという事に基づきます。先に見たパワーステージと抵抗分割部とこのエラーアンプと補償器のステージの合計のゲインが目標クロスオーバー周波数で1(0dB) になる様にこのステージでのゲインをRcで決める事になります。このゲインはエラーアンプのトランスコンダクタンス(Gea) * Rc で簡略化されます。

それでは今回の例では既に答えは出ておりますが、補償器の合成インピーダンスを計算しながら何故 Rc だけが目標クロスオーバー周波数でのゲインを決める事になるのかを見ていきましょう。

8. エラーアンプステージの Fco(60kHz) でのインピーダンスとゲインを計算する

Ccの60kHzでのリアクタンスは、

これとRcとの直列合成インピーダンス Zrc+cc は、

となり、Ccは無視でき、Rcだけであるとシンプル化出来ます。

Ccpの60kHzでのリアクタンスは、

となり、Rcに比べると無視できるほど大きいので、無いもの(無限大)とシンプル化出来ます。 つまりこのステージの Fco(60kHz) におけるインピーダンスは Rcの31.6kΩだけであると考えられます。60kHzでのゲインは、

となります。

9. Rc の計算式

ここまでに見てきたFcoでのパワーステージ・ゲイン (Av(ps) = 0.630) と抵抗分割部のゲイン (Av(fb) = 0.181) はどちらも変える事は出来ません。これにエラーアンプ・補償器のゲイン(Av(ea) ) を掛けたものが総合ゲインになります。そして私達は総合ゲインをFcoで 1 (0dB) にしたいので、次の関係式が導かれます。

![]()

これより

で計算できます。

設計した位相補償は正しいのか?(シミュレーション編)

ここまでで、位相補償の基本的な考え方と定数の求め方を解説しました。

では、この設計は実際に安定動作するのでしょうか?

次はシミュレーションでその動作を確認していきます。

▶ DC/DCコンバータの位相補償の学び(Part2)はこちら

DC/DCコンバータやAnalogDevices製品についてのお問い合わせはこちら

メールマガジンの登録はこちら

定期的に技術情報やセミナー等の案内をしていますので、ぜひご登録お願いします。